如何正确理解采样时钟抖动对ADC信噪比的影响

前言:本文介绍了模数转换器采样时钟的抖动参数对模数转换器采样的影响,主要介绍了以下内容:

时钟抖动的构成

时钟抖动对ADC SNR的影响

如何计算时钟抖动

如何优化时钟抖动

1.采样理论

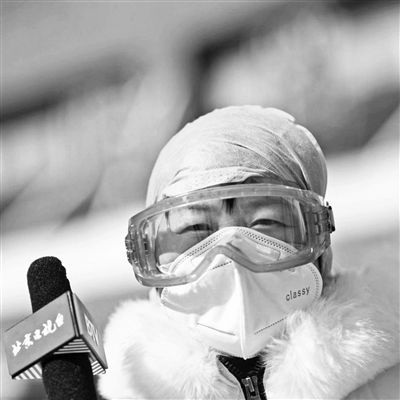

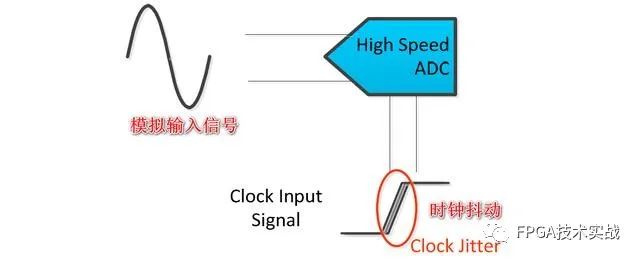

高速模数转换器使用外部输入时钟对模拟输入信号进行采样,如图1所示。图为输入采样时钟抖动示意图。

图1。模数转换器采样

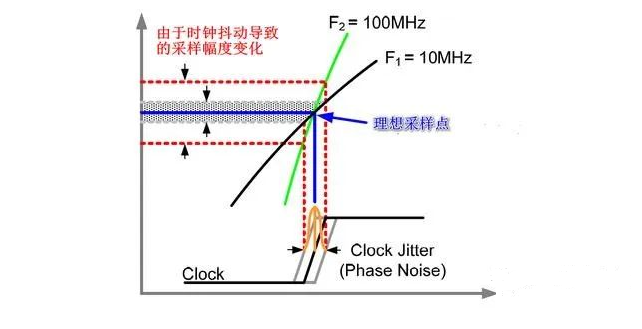

输入模拟信号的频率越高,由时钟抖动引起的采样信号的幅度变化越大,这在图2中非常明显。当输入信号频率为F2=100MHz时,采样幅度的变化明显大于输入信号频率为F1=10MHz时的变化。

图2。时钟抖动对不同频率输入模拟信号的影响

2.采样时钟抖动

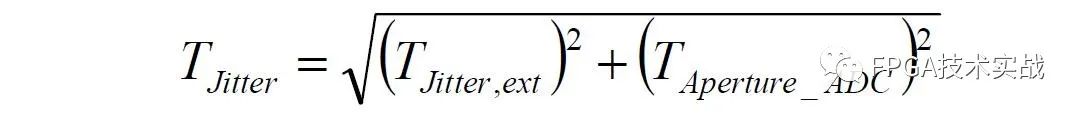

采样时钟抖动主要由两部分组成:

外部输入时钟抖动

模数转换器孔径抖动

图3。时钟抖动计算公式

时钟边沿速率越快,时钟抖动越小,设计PCB越困难。

图4。时钟抖动成分

3.时钟抖动对信噪比的影响

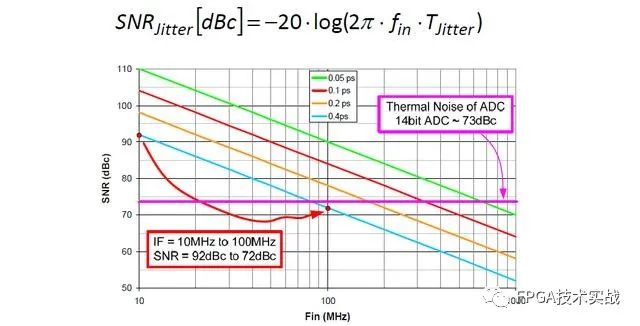

时钟抖动对ADC信噪比的影响由图5所示公式计算。在图5中,可以看出时钟抖动对高频模拟输入信号的影响更大。

图5。时钟抖动对信噪比的影响

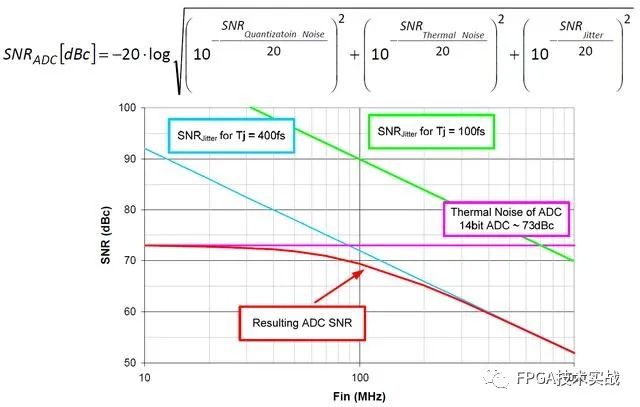

模数转换器噪声下限信噪比通常由三部分组成:

模数转换器量化噪声

模数转换器热噪声

抖动衰减

图6。模数转换器噪声下限的计算

4.计算抖动幅度

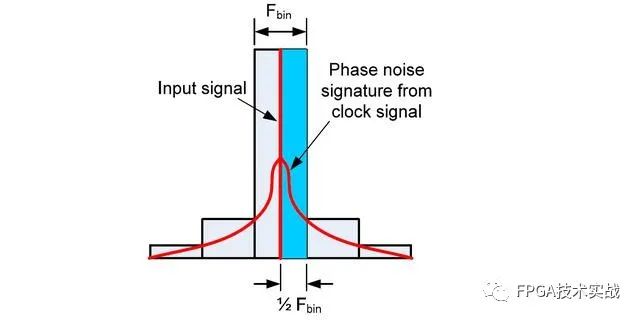

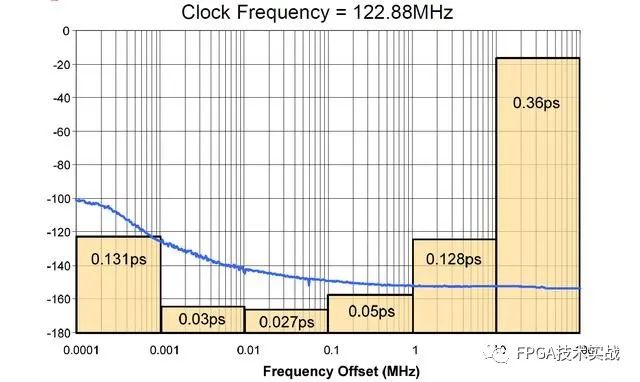

时钟抖动是通过对时钟信号的相位噪声进行积分获得的。典型的计算应用需求如图7所示。

图7。典型时钟抖动计算要求

积分上限一般受以下因素限制:

时钟滤波器带宽

模数转换器时钟输入带宽

模数转换器采样速率

图8。对应于时钟频率偏移的抖动值

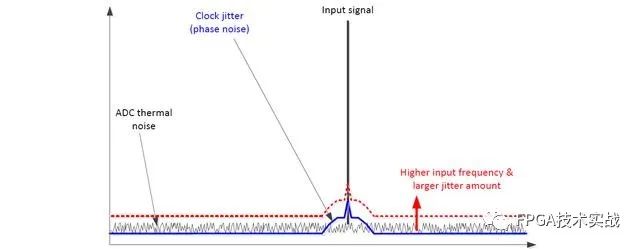

5.SRN在频率的影响

在采样过程中,时钟信号的相位噪声被添加到输入信号中。输入信号频率越高,相位噪声幅度越大,相位噪声越大,ADC的噪声下限越差,ADC的有效分辨率越低。

图9、相位噪声在频率的频谱图

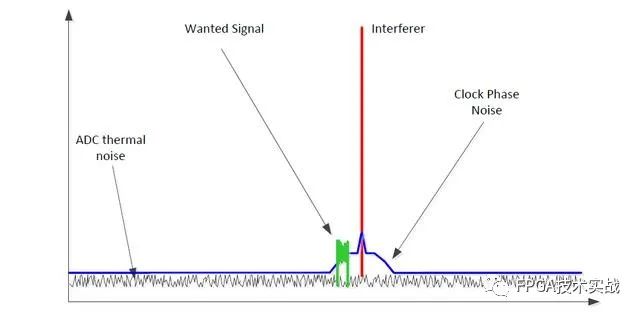

6.为什么时钟抖动/相位噪声如此重要

典型接收机在“阻塞条件”下的性能包括两个方面:

首先,接收机需要在噪声背景中检测所需的小信号

第二,在无法滤波的频带中存在较大的干扰,这将影响小信号检测

图10。时钟抖动增强了带内干扰的影响

7.如何优化时钟抖动性能

为了最大化给定模数转换器的信噪比性能,系统设计人员可以采取几个步骤:

使用低抖动/相位噪声时钟源

具有低插入损耗的带通滤波器用于限制宽带噪声衰减

确保时钟幅度足够,并且不会降低模数转换器孔径抖动

编辑:jq

延伸 · 阅读

- 2021-04-07 17:31国星光电积极践行“对标世界一流管理提升行动”推动数字

- 2021-04-07 17:31互联网行业总体平稳,挑战与机遇并存

- 2021-04-07 17:31中芯国际2020年Q1财报出炉 营收创新高且资本支出上调

- 2021-04-07 17:31在西门子EDA系列研讨会上回顾如何提高电子设计效率

- 2021-04-07 17:31BLE低功耗蓝牙或可检测的社交距离

- 2021-04-07 17:31制动电机是如何工作的 它是如何调节制动器的