基于时钟发生器的时钟树解决方案

随着数据速率的提高,对参考时钟的需求也在增加。本文将重点讨论参考时钟要求。

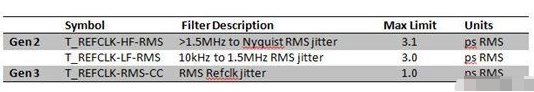

PCIe参考时钟(RefClk)规范可针对三种不同的架构进行定义:数据时钟、独立RefClk和通用RefClk。每种架构都有特定的过滤功能。出现在接收机时钟数据恢复输入端的有效抖动是接收机和发射机锁相环带宽之差以及RefClk抖动频谱峰值的函数。此外,它还取决于RefClk架构。

在独立RefClk架构中,发射机(TX)和接收机(RX)都可以接收独立的RefClk。这导致了严格的抖动要求,不能应用扩频时钟(SSC)。

在数据时钟架构中,单个RefClk可以连接到发射器,而接收器使用数据流中的嵌入式时钟信号。时钟数据恢复(CDR)电路可以提取数据流中的时钟。它最大限度地缓解了抖动要求,也可以应用SSC。但是这是一个比较新的标准,很多设备都不支持。

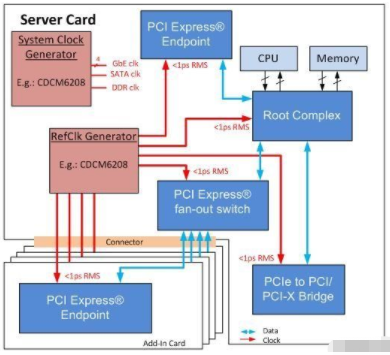

最佳替代标准(也是最常用的标准)是通用RefClk架构。它不仅可以为发射机和接收机提供相同的RefClk,还支持SSC,可以减少电磁干扰(EMI),实现非常方便。这种架构的缺点是RefClk需要满足小于12ns的失调要求。下面是一个通用的RefClk架构及其应用实例。

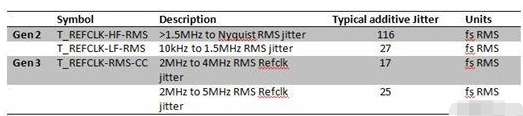

表2:应用滤波器功能后的通用RefClk抖动规格

图1:解决方案1:支持第三代PCIe通用参考时钟抖动限制的服务器卡示例

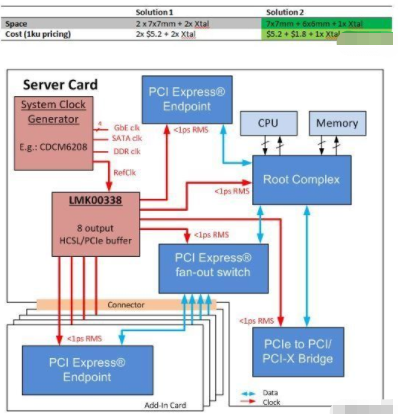

图1所示的系统可以使用7输出时钟发生器来实现。这样的实现可能最终需要基于时钟发生器的不止一个时钟树解决方案,因为需要生成其他系统时钟。系统时钟发生器可以为千兆以太网设备、SATA控制器、DDR时钟等生成参考时钟。在图2中,RefClk发生器由时钟缓冲器代替。这不仅简化了时钟树,还提供了一种成本更低、空间更优化的解决方案。

表3:解决方案1和解决方案2的比较以及空间和成本

图2:解决方案2:使用RefClk缓冲区(如LMK00338)的服务器卡实例容量

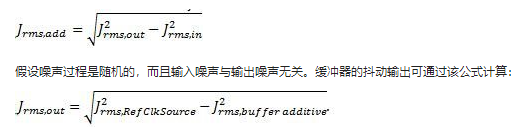

使用缓冲器分配RefClk时,需要考虑缓冲器引起的额外抖动。额外抖动的定义是器件本身对输入信号造成的额外抖动量。计算方法如下:

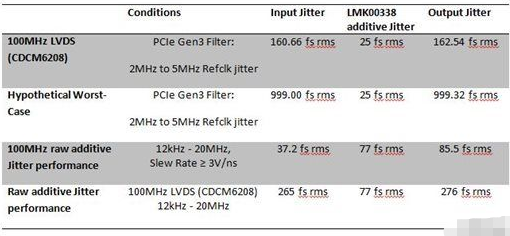

LMK00338是一款超低额外抖动PCIe时钟缓冲器。对于第三代PCIe应用,通常会有30fs rms的额外抖动。表3显示了应用不同PCIe滤波函数时的附加抖动性能。

表4:4:LMK 00338的附加抖动性能

CDCM6208等第三代PCIe高性能时钟发生器可提供均方根抖动为160.66 fs的RefCLK(2 MhZ至5MHz滤波器)。如果分配了该时钟,LMK00338将向RefClk信号添加25fs均方根抖动。根据上述公式计算的输出抖动仅为162.54 fs rms(表5)。在最坏的情况下,RefClk发生器的抖动可能为999fs rms,使用LMK00338不会超过第三代PCIe的抖动限值。

表5显示了LMK00338在未应用PCIe滤波功能时的额外抖动性能。该缓冲器具有77 fs rms的低额外抖动(集成带宽:12kHz至20MHz),适合使用HCSL信号传输技术的大多数高性能时钟应用。也有较小的4输出版本。

表5:低抖动RefClk源(CDCM6208)驱动的时钟缓冲器的效果。

多个服务器卡的一个常见问题是电源噪音。噪声可能来自多个噪声源,首先是开关电源和CPU、ASIC或FPGA等数字电路。电源旁路将有助于滤除部分噪声,而剩余噪声将影响器件性能。当残余噪声影响时钟分配器件的供电时,会导致时钟输出的窄带调相和调幅。

在100千赫兹至10兆赫兹的噪声频率范围内,LMK00338在100兆赫兹的输出频率下可以表现出低于-75分贝的出色PSRR性能。这种抗扰度将有助于简化电源旁路,这是LMK00338的另一个重要优势。

以上分析表明,只要RefClk发生器满足抖动要求,就可以安全大胆地使用一般RefClk系统中的超低附加抖动时钟缓冲器。

此外,LMK00338的通用输入级不仅可以接收任何差分或单端信号,还可以将其转换为8 HCSL输出。对于第四代PCIe,最大RefClk抖动可以假设为远小于1ps rms。因此,支持缓冲的通用RefClk架构将更适合更严格的新PCIe标准。

负责编辑:gt

延伸 · 阅读

- 2021-06-28 17:31光电二极管电路的漏电流和带宽分析

- 2021-06-28 17:315G将成为后疫情时代助力各企业复工复产、冲出重围的有力

- 2021-06-28 17:31Starlight:尝试通过VR代替儿童手术全身麻醉方案

- 2021-06-28 17:31圣智AI硬核技术护航冬奥会

- 2021-06-28 17:31芯片短缺何时才能缓解?

- 2021-06-28 17:31什么是智能开关 智能开关的原理是什么?