在无线应用设计中选择操作系统时应该考虑哪些因素

作者:顾源,西林传播事业部高级经理

随着无线数据吞吐量的爆炸式增长,数字信号处理技术和无线电设备面临着巨大的改进压力。目前的重点是4G LTE。4G网络正在世界范围内大规模部署。而现在我们看到5G网络的前期研发工作已经开始,其目标是在4G网络的基础上增加数千倍的数据容量。这项新技术的发展对系统制造商提出了新的要求。他们必须提高系统集成和系统性能,降低系统物料清单(BOM)成本,提高设计灵活性,并加快产品上市过程。

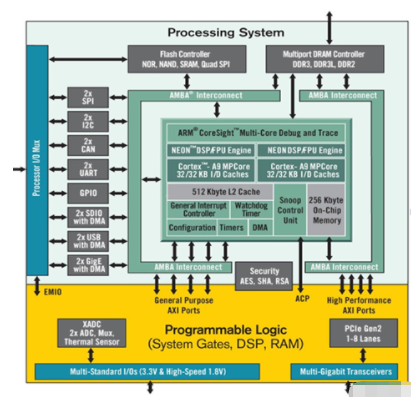

虽然传统的专用集成电路设备支持的硬件解决方案可以实现功耗和成本目标,但偶尔的工程成本(NRE)极高,灵活性差,产品推出过程非常慢。为了满足这些要求并应对这些挑战,Xilinx向业界推出了全可编程片上系统(APSoC)架构,并在Zynq-7000产品系列中成功实施。

图1: ZYNQ-7000全可编程片上系统架构

在构建基于Zynq APSoC设备的无线应用时,需要选择能够满足应用需求的操作系统。因此,对于不同的无线应用,需要考虑几个关键因素:

1.电信级运营能力:对于电信级系统,一般要求系统可靠性达到99.999%。机组在正常工作时间的可靠性肯定这么高。从操作角度来看,它代表了对系统各种特性的支持,如冷/热启动、故障监控、检测和处理以及冗余。

2.实时处理:实时意味着可预测的响应时间,而不仅仅是“非常快”。与无线回程处理相比,远程射频单元有不同的实时要求。无线电设备具有繁重的信号处理任务,用于支持信号处理的处理器必须满足严格的时序预算要求。

3.诊断:为了支持现场诊断和事后诊断,需要收集和存储大量的性能测量数据和日志数据。因此,它应该能够跟踪和管理一些对无线应用非常重要的关键指标,如性能测量和统计指标、CPU利用率和故障监控指标、OS任务切换指标和事件历史指标。

4.工具和协议的集成:调试和诊断环境的综合集成,加上一些OS厂商提供的一些特定的网络协议栈,有助于设计人员开发和维护有效的系统。

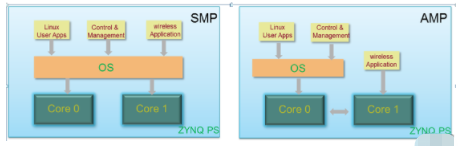

Zynq SoC集成了两个ARM Cortex A9内核。软件架构师需要在目前支持的两种多处理器架构之间进行选择:SMP(对称多处理)或AMP(非对称多处理)。如图2所示,在SMP系统架构中,两个或更多相同的处理器共享资源并运行操作系统实例。理论上,这种架构将平等对待同一操作系统实例下的所有处理器。相反,AMP架构对每个处理器的处理都是不同的,不管是否有OS实例,处理器都是相互隔离的。不运行操作系统的内核可能正在运行一段微码,该微码被视为“裸机”实例。

一般来说,SMP为更高级别的应用提供了统一的OS平台。在OS上构建应用时,软件架构师不需要考虑两个内核之间的资源共享和进程间通信。此外,SMP还存在性能开销,这将对时间关键型无线应用的性能产生不利影响。相比SMP和AMP,AMP在运行OS实例时软件更简单,基本上完全没有开销问题,但是需要精心定制的软件设计来实现处理器资源共享和处理器间通信。

图2:2的比较:SMP和AMP

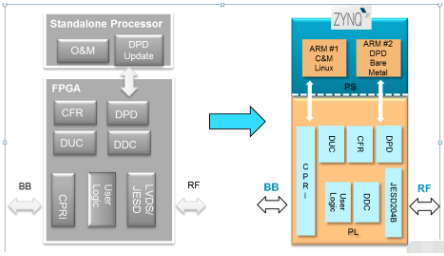

许多关键的无线应用,包括射频和无线回程,都可以通过Zynq APSoC设备非常高效地实现。每个无线应用都有不同的性能要求,要求OS支持不同的特性。就使用Zynq实现覆盖所有数字前端和处理功能的全集成软硬件解决方案而言,射频应用就是一个很好的案例。

射频数字前端的应用是4G网络中典型远程射频单元(RRH)的主要组成部分。本应用的处理要求可分为信号处理和控制处理。在信号处理领域,Zynq可用于实现高采样率滤波器、峰值因子抑制(CFR)和数字预失真(DPD),以实现数字上/下转换。DPD是个特例,它需要同时使用Zynq PS和PL。

DPD处理可以细分为高速数据路径和更新路径。更新路径用于周期性更新滤波器组的系数,非常适合在ARM Cortex A9内核中实现。一般来说,系数更新必须在几毫秒到几十毫秒内完成。鉴于计算的算法复杂性,A9内核和嵌入式NEON SIMD矢量计算单元可以综合使用,以满足所需的高性能。此外,Zynq PL还支持对处理器时钟周期占用较大的功能进行硬件加速,使得Zynq PL、ARM A9内核和NEON协处理器可以协同使用。

收音机的控制处理端一般用于收音机的初始校准、配置、报警、调度和网络消息下载。一般来说,这在无线电应用中不需要高性能,因此可以通过在Zynq中使用ARM A9内核来轻松管理。

选择合适的架构来支持DPD应用和控制处理应用非常重要,因为它决定了整体性能、可靠性和易于维护性。

选择射频应用

的通用架构是AMP模式。在这种模式下,一个完整的ARM内核以裸机方式运行,专门用于DPD处理,为满足更新DPD系数的时间要求提供更大计算裕量。控制和OAM等其他应用运行在OS控制的第二个ARM A9核上。在这种架构中,由于OS只控制两个ARM内核中的一个,必须在运行于两个分离的内核上的应用之间建立处理器间通道,比如使用OCM(片上存储器)或共享存储器。这样做法对某些关键的控制应用非常重要,比如用于监控DPD模块健康状况的应用。这样进程间通信(IPC)解决方案是非标的,必须在AMP模式中单独开发。SMP架构非常简单直观,使用单个OS实例同时控制两个ARM内核和,进而控制全部应用。IPC、调试、支持工具链都在同一OS下。为确保资源专门用于DPD应用,可在软件应用中使用“内核亲和(Core Affinity)”和“中断屏蔽”等专门技巧。在前一个案例中,DPD应用将只在一个内核上运行,也就是没有其他任务共享资源(除去OS调度器开销)。在后一个案例中,中断服务(除DPD应用触发的)被转到第二个内核上运行。这样资源就被DPD应用完全利用。

因此Zynq APSoC是支持AMP或SMP架构的理想平台。如图3所示,Zynq集成有双内核ARM处理器、12.5Gb/s 串行收发器(SerDes)、可靠性更高的500MHz+ DSP,并能提供完整的数字前端功能,诸如DPD、CFR、DUC/DDC和CPRI/JESD接口。该解决方案无需在处理器和单独FPGA之间提供接口,从而简化PCB设计。

从分立式多芯片解决方案移植到Zynq平台上的单芯片集成解决方案非常简单直观。赛灵思提供综合而全面的软硬件解决方案,有助于顺利移植到Zynq上。这其中包括用于DUC、DDC、CFR和DPD的数字信号处理IP库。此外,还支持多种OS解决方案,包括设备驱动程序、引导载入程序、BSP模板和常用工具。在成功移植到Zynq平台后,该解决方案能够显著地增强系统性能,节省总功耗,并降低材料清单(BOM)成本。

图3:从分立式解决方案移植到Zynq解决方案

在本文中,我们探讨了为无线应用选择操作系统应考虑的主要因素,无线应用的实现架构及其考虑因素(AMP与SMP对比)以及上述在赛灵思Zynq 7000器件上的直接应用。总之,赛灵思提供的这类先进器件能够帮助无线网络基础架构设计人员在实现软硬件完全可编程性的同时,改善性能,提高系统集成度,降低材料清单(BOM)总成本与系统总功耗,实现高可靠性并加速产品上市进程。设计人员现在不仅能更快开发设备,而且还能在设备部署完成很久之后继续提供现场更新,从而避免与ASSP和ASIC等器件有关的风险。

责任编辑:gt

延伸 · 阅读

- 2021-06-29 18:14Intel DG2独立显卡曝光 基于Intel 7nm EUV工艺打造

- 2021-06-29 18:14电网规划与改造要有弹性?

- 2021-06-29 18:14墨子号实现世界首次千公里级基于纠缠的量子密钥分发

- 2021-06-29 18:14NVIDIA GPU服务器和软件框架解决IDC机房数字化问题

- 2021-06-29 18:14变压器漏油的原因是什么?

- 2021-06-29 18:14元宇宙依赖什么技术_元宇宙的技术支柱