数据信号和DQS有什么关系

在上一篇文章中,我们使用了仿真示例来显示DDR中地址相对于时钟的建立时间和保持时间。那么数据信号和DQS有什么关系呢?众所周知,DDR的速度是普通SDRAM的两倍。这个怎么理解?原来,SDRAM在写入或读取数据时是由上升沿或下降沿触发的。

请注意,这里只是上升沿或下降沿,并非上升沿和下降沿同时有效。如果时钟频率为800MHz,对应的数据速率为800Mbps。然而,DDR的数据信号具有双倍的速率。如果DQS频率为800兆赫兹,数据信号速率应为1600兆位/秒。

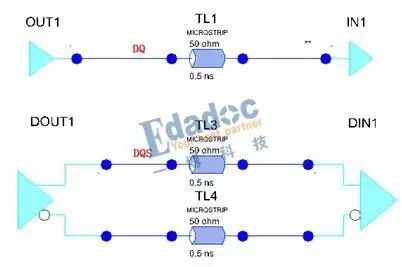

让我们通过一个具体的仿真例子来看看。

图1 DQ和DQS模拟示意图

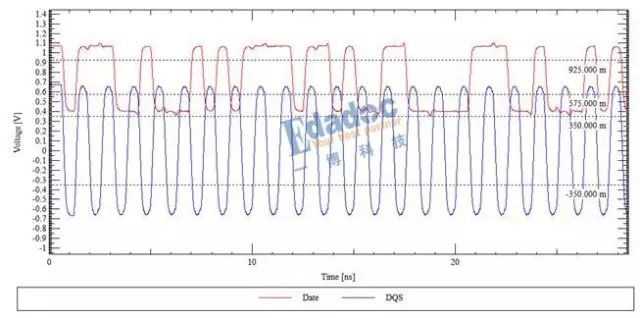

仿真通道如上图所示。驱动器和接收器均为某芯片公司的IBIS型号,仿真波形如下:

图2 DQ和DQS模拟波形

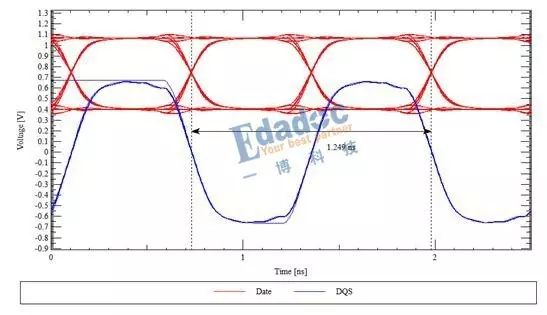

我们同时生成DQS和DQ信号的眼图,并在窗口中观察它。结果如下:

图3 DQ和DQS眼图

在这里,作者最初想模拟DDR写操作期间DQS和DQ之间的时序对应。在前一篇文章中,我们知道在写入操作中使用高低电平的中点作为触发点,上面眼图中的波形对应显然不能完成数据的写入,因为DQS的边缘基本上与数据信号反转的边缘对齐。

在仿真中,两个波形简单地放在一起,因为DQ和DQS的传输通道长度相同,所以它们的边缘对齐。在实际工作中,主控芯片会有一个调节机制。一般来说,数据信号将比DQS提前四分之一周期发布。事实上,在粒子端接收到的波形对应应该如下:

主控芯片调整后,DQS边缘对准DQ信号位中心,可以保证数据传输到接收端时有足够的建立时间和保持时间。即使DQS和DQ之间的线长匹配没有那么严格,也会有一定的时序余量。

话虽如此,其实我们要解决的根本问题是长度匹配的范围。了解了这些基本问题之后,我们需要做的就是把这些时间参数转化为延迟。如何计算线长的匹配范围?让我们举一个具体的例子来看看时序裕量是如何计算的。我们先简单看一张图片

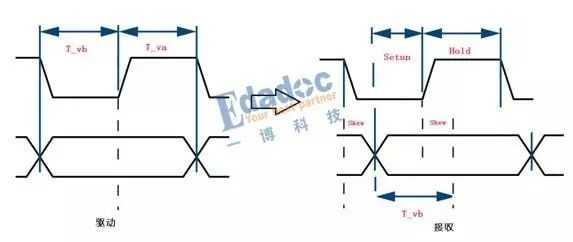

延迟偏差对时序的影响

在上图中,T_vb和T_va代表主芯片输出数据时时钟和数据之间的时序参数。在理想情况下,时钟边沿和数据电平中心对齐。因为时钟和数据传输通道的长度不相等,所以时钟边沿不与数据脉冲的中间位置对齐,这使得建立时间的余量很小。

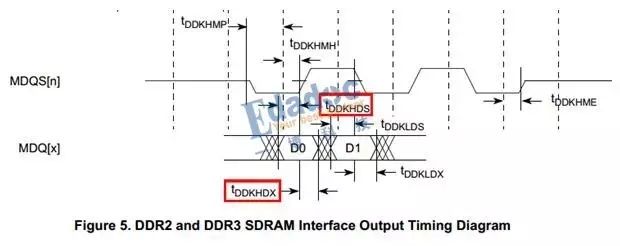

让我们通过一个具体的例子来看看时序计算。下图是飞思卡尔MPC8572 DDR主控芯片说明书。这张图定义了DQS和DQ从芯片出来时的相位关系。

MPC8572序列图

粒子端为Micron DDR,芯片的时序图和时序参数如下图所示,定义了粒子端芯片识别信号所需的建立时间和保持时间。

我们用T_pcbskew来表示DQ和DQS之间的延迟偏差。如果我们想获得足够的时序裕量,延迟偏差应满足以下关系:

《T_vb-T_setup》

T _ pcbskew”T _ hold-T _ va

替代数据包括:

T_vb-T_setup=375-215=160ps

T_hold-T_va=-160ps

这样,如果输电线路速度计算为6mil/ps,T_pcbskew为/-960mil。你会发现利润很大。当然,这只是最好的情况,不考虑时钟抖动、数据信号抖动、串扰和码间干扰。如果将这些因素考虑在内,布线偏差的余量将相对较小。

延伸 · 阅读

- 2021-07-23 16:45Apple Watch Series 6或有告知惊恐症发作的新功能

- 2021-07-23 16:45全新的混合云部署方案,可满足用户多样化的需求

- 2021-07-23 16:45深耕20年:助力运营商降本增效

- 2021-07-23 16:452020年Q1手机UI排行榜:一加氢OS超过150分排在榜首

- 2021-07-23 16:45OpenHarmony Dev-Board-SIG专场:主码三方芯片支持目录整改

- 2021-07-23 16:454321理论教你如何完成结构强度分析