探究仿真仿真-波形状态机名称显示

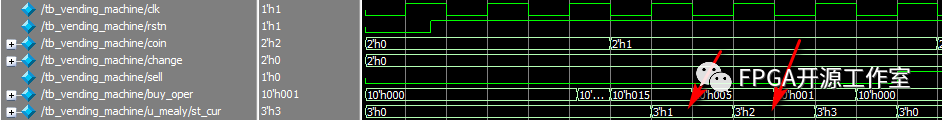

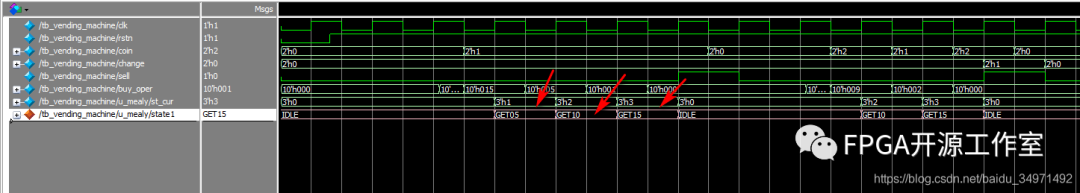

在通常的仿真波形仿真中,状态机的显示为16进制,如3'h1。如下图所示str_cur为状态跳变信号。

为了更加直观的以文本形式显示状态机的跳变,如自己定义的闲置的等,我们可以使用

虚拟类型虚拟函数

状态机源文件:

//自动售货机//2元一瓶饮料//只支持2个硬币:5角一元//完成售卖和兑换功能

模块自动售货机_机器(输入clk,输入rstn,输入[1:0]硬币,//01为0.5角,10为一元

输出[1:0]变化,输出出售/输出这饮料);

//机器状态解码参数空闲=3 ' d0参数GET05=3 ' d1参数GET10=3 ' d2参数GET15=3 ' d3

//机器变量reg[2:0]ST _ cur;

//(1)使用一个状态变量描述reg[1:0]change _ r;reg sell _ r;总是@(posedge clk或negedge rstn)开始if(!rstn)开始ST _ cur "=' B0change _ r "=2 ' B0sell _ r "=1 ' B0end else begin case(st_cur)

IDLE:begin change _ r "=2 ' B0;sell _ r "=1 ' B0表壳(硬币)2 ' b01:ST _ cur "=GET05;2 ' b10:ST _ cur "=GET 10;结束案例结束GET05:开始案例(硬币)2 ' b01:ST _ cur "=GET10;2 ' b10:ST _ cur "=GET 15;端盖端

GET 10:case(硬币)2 ' b01:begin ST _ cur "=GET 15;end 2 ' b10:begin ST _ cur "=IDLE;sell _ r "=1 ' B1末端外壳

GET15:case(coin)2 ' b01:begin ST _ cur "=IDLE;sell _ r "=1 ' B1end 2 ' b10:begin ST _ cur "=IDLE;change _ r "=2 ' B1sell _ r "=1 ' B1末端外壳

默认值:begin ST _ cur "=IDLE目标

endcase //case (st_cur) end //else:if(!rstn)结束

赋值sell=sell _ r;分配变更=变更_ r;

末端模块

仿真顶层文件:

`时间刻度1ns/1ps

模块tb _自动售货机;

reg clkreg rstnreg [1:0]硬币;电线[1:0]更换;电汇销售;

//时钟生成参数CYCLE _ 200MHz=10//总是开始clk=0;#(CYCLE _ 200 MhZ/2);clk=1;#(CYCLE _ 200 MhZ/2);目标

//动机生成reg[9:0]buy _ oper;//购买操作的存储状态初始begin buy _ oper=' h0硬币=2 ' h0rstn=1 ' B0 # 8 rstn=1 ' B1 @(neg edge clk);

//case(1)0.5-》0.5-》0.5-》0.5 # 16;buy _ oper=10 ' b00 _ 0101 _ 0101重复(5)begin @(neg edge clk);coin=buy _ oper[1:0];《买入操作=买入操作》2;目标

//案例(2) 1 -》 0.5 -》 1,取变化# 16;buy _ oper=10 ' b00 _ 0010 _ 0110重复(5)begin @(neg edge clk);coin=buy _ oper[1:0];《买入操作=买入操作》2;目标

//case(3)0.5-《1-》0.5 # 16;buy _ oper=10 ' b00 _ 0001 _ 1001重复(5)begin @(neg edge clk);coin=buy _ oper[1:0];《买入操作=买入操作》2;目标

//案例(4)0.5-〉0.5-〉0.5-〉1、取变化# 16;buy _ oper=10 ' b00 _ 1001 _ 0101重复(5)begin @(neg edge clk);coin=buy _ oper[1:0];《买入操作=买入操作》2;结束结束

自动售货机u_mealy(.clk (clk),rstn .硬币。改变(改变),出售(出售));

//模拟完成总是从#100开始;if($ time)=10000)$ finish;目标

endmodule /测试

仿真脚本sim.do文件:

#建立一个新的图书馆

#切换到仿真源文件目录

vlog ACC " TB _ venting _ machine。v“vlog ACC”通风_机器。“五

#开始模拟

vsim-VOP targs=ACC工作。结核病_自动售货机

#把顶层的所有信号加起来波* #做波。做

虚拟类型{ {0x 00 IDLE } {0x 01 GET 05 } {0x 02 GET 10 } {0x 03 GET 15 } } FSM _ TYPe虚拟函数{(FSM _ TYPE)/TB _ autowing _ machine/u _ mealy/ST _ cur }状态1添加wave u _ mealy/ST _ curad wave-color pink/TB _ autowing _ machine/u _ mealy/状态1

视图结构视图信号全部

仿真结果如下

状态机二进制被文本所替代。

编辑:jq

延伸 · 阅读

- 2021-07-23 16:49快讯:特斯拉联合宁德时代今年底推低成本电池

- 2021-07-23 16:49嵌入式微处理器在线不间断电源的设计

- 2021-07-23 16:495G核心网系统的简要概述

- 2021-07-23 16:49全球首台"5G+8K"超高清视频全业务转播车精彩亮相

- 2021-07-23 16:49摆脱大国阴影 加拿大半导体30年计划

- 2021-07-23 16:49TBAC的组成结构及在图书馆管理系统中的应用研究