全加器逻辑表达式_全加器的逻辑功能

全加器逻辑表达式

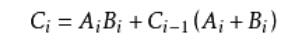

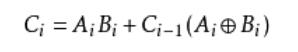

一位全加器的表达式如下:

Si=Ai⊕Bi⊕Ci-1

第二个表达式也可来用一个异或门来代替或门对其中两个输入信号进行求和:

其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci。一位全加器可以处理低位进位,并输出本位加自法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

全加器的逻辑功能

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数![]() 和

和![]() ,还有一个来自前面低位送来的进位数

,还有一个来自前面低位送来的进位数![]() .这三个数相加,得出本位和数(全加和数)

.这三个数相加,得出本位和数(全加和数)![]() 和进位数

和进位数![]() .这种就是“全加“,下表为全加器的逻辑状态表。

.这种就是“全加“,下表为全加器的逻辑状态表。

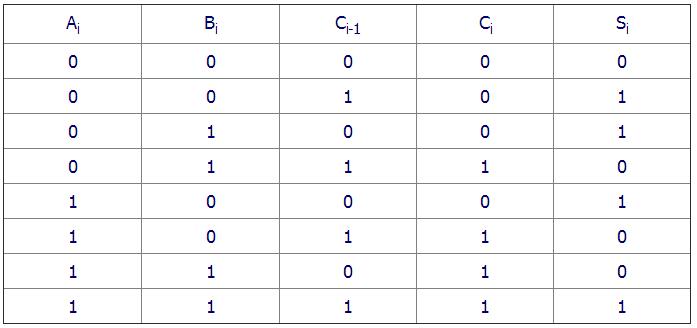

全加器可用两个半加器和一个“或“门组成。

如上图(a)所示。![]() 和

和![]() 在第一个半加器中相加,得出的结果再和

在第一个半加器中相加,得出的结果再和![]() 在第二个半加器中相加,即得出全加和

在第二个半加器中相加,即得出全加和![]() 。两个半加器的进位数通过”或“门输出作为本位的进位数

。两个半加器的进位数通过”或“门输出作为本位的进位数![]() 。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

延伸 · 阅读

- 2020-04-23 11:13教你如何消除步进电机的噪音和振动

- 2020-04-23 11:13游族网络发布2021年半年报:营收17.67亿元,净利润达2.63亿元

- 2020-04-23 11:13蘑菇车协会“车陆云一体化”自动驾驶方案

- 2020-04-23 11:13哪款蓝牙耳机的颜值更高?高价值蓝牙耳机评估

- 2020-04-23 11:13国家千人 计划专家洪锦维携手茶饮教父郭文河抢攻5G直播商机

- 2020-04-23 11:13STM32有两个看门狗 独立看门狗和窗口看门狗